# Discussion 4

Jan 30

### Outline

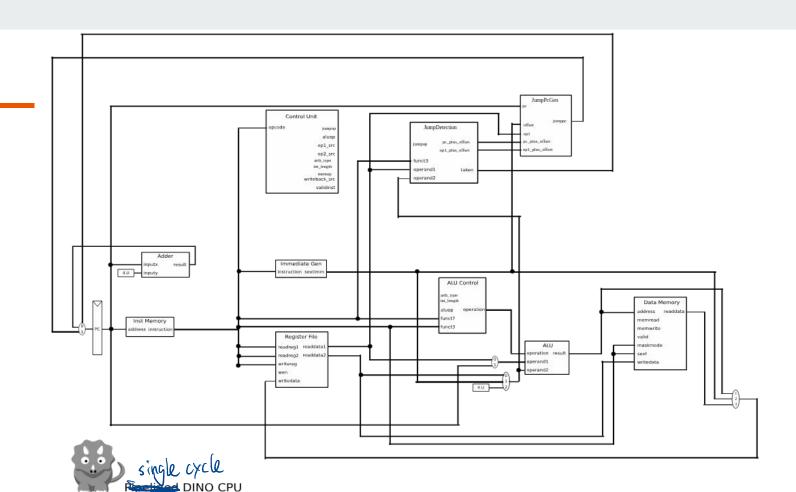

- 1. DINOCPU assignment 3.1

- 2. Week 4 quiz

## Week 4

| Question 1                                        | Question 2               |                        | Question 3                                                           |

|---------------------------------------------------|--------------------------|------------------------|----------------------------------------------------------------------|

| The effective address is used to access memory    | The ALU generates a      | result value           | Bits from the instruction are used to choose which registers to read |

| ○ execute                                         | ○ writeback  ✓ execute   |                        | o execute memory                                                     |

| ○ fetch                                           |                          |                        |                                                                      |

| memory                                            | ) memory                 |                        | ○ fetch                                                              |

| ○ decode                                          | ○ fetch ○ decode         |                        | ✓ decode  ○ writeback                                                |

| ○ writeback                                       |                          |                        |                                                                      |

| Question 4                                        |                          | Question 5             |                                                                      |

| Retrieve 32 bits of data from memory which corres | ponds to the instruction | The processor generate | es control signals for the instruction                               |

| ○ writeback                                       |                          | ○ memory               |                                                                      |

executefetch

decode

writeback

memory

○ decode

execute

|              | Vala path                                                 |

|--------------|-----------------------------------------------------------|

| [ Select ]   | Jata Path<br>is shared by all instructions.               |

| [ Select ]   | control tath.                                             |

| control path | CONKI OI TO                                               |

| data path    | selects subsets of components to use for each instruction |

| Question 10                                                                     | 1 p        |

|---------------------------------------------------------------------------------|------------|

| "A state element that contains a set of locations that can be read/written by s | upplying a |

| location number and that is usually accessed multiple time for each instruction | describes  |

| which of the following data path elements?                                      |            |

| ○ Immediate generator                                                           |            |

| ○ PC                                                                            |            |

| ○ Muxes                                                                         |            |

| ○ Instruction memory                                                            |            |

| Register file                                                                   |            |

| ○ ALU                                                                           |            |

| ○ data memory                                                                   |            |

| ○ control unit                                                                  |            |

Question 11 2 pts

There is a processor design that combines some steps. It has three stages: fetch & decode, execute, and memory & writeback. Use the following information to answer the question.

Note: This may be different from other questions.

#### Fetch & Decode Execute Memory & Writeback

160ps 250ps 100ps

If this is a single-cycle processor design, what is the cycle time of this processor in ps?

100+160 +250 = 510 ps.

Question 12 2 pts

There is a processor design that combines some steps. It has three stages: fetch & decode, execute, and memory & writeback. Use the following information to answer the question. Note: This may be different from other questions.

#### Fetch & Decode Execute Memory & Writeback

160ps 160ps 240ps

What is the CPI for this processor?

Question 13 2 pts

There is a processor design that combines some steps. It has three stages: fetch & decode, execute, and memory & writeback. Use the following information to answer the question. Note: This may be different from other questions.

#### Fetch & Decode Execute Memory & Writeback

200ps 230ps 270ps

How long does it take to execute an application with 6 billion instructions on this single cycle processor (in seconds)?

exetime = #\(\text{inst} \times CPI \times \text{cycletime.}\)

$$6 \times 10^{4} \times 1 \times 700 \times 10^{-12}$$

| Question 14                                                                                                                                                                  | ts Question 16 1 pts                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| How long does it take to complete a single load of laundry (in minutes)?  Pre-wash Washing Drying Folding/hanging  50 min 60 min 50 min 60 min $50 + 60 + 50 + 60 = 220$ WW. | What is the cycle time for the pipelined laundry (in minutes)? I.e., how frequently will a load be finished?  Pre-wash Washing Drying Folding/hanging 60 min 60 min 40 min 40 min  60 m(v) |

| Question 15                                                                                                                                                                  | ts Question 17 1 pts                                                                                                                                                                       |

| What is the limiting "stage" for this laundry system? (Can have multiple answers)?  Pre-wash Washing Drying Folding/hanging                                                  | What is the throughput for the pipelined laundry? I.e., how many loads can you complete per hour?  Pre-wash Washing Drying Folding/hanging                                                 |

Pre-wash

☐ Drying

Washing

☐ Hanging/folding

**Question 18** 1 pts What is the speedup pipelining compared to not pipelining? Assume you only care about the steady state (i.e., no need to consider warmup/cooldown time). Pre-wash Washing Drying Folding/hanging 50+50+60+60) 50 min 50 min 60 min 60 min 220 Question 20 What is the limiting stage for this pipeline? (Can have multiple answers)? Fetch Decode Execute Memory Writeback 500 ps 500 ps 200 ps 400 ps 400 ps ☐ Writeback Memory Fetch ☐ Execute Decode

#### Question 19

How long does it take to execute a single instruction? (in ps)

Fetch Decode Execute Memory Writeback

600 ps 500 ps 400 ps 600 ps 400 ps

600+500+400+600+400.

#### Question 21

What is the cycle time for the pipelined processor?

Fetch Decode Execute Memory Writeback

600 ps 500 ps 200 ps 500 ps 400 ps

600 PS

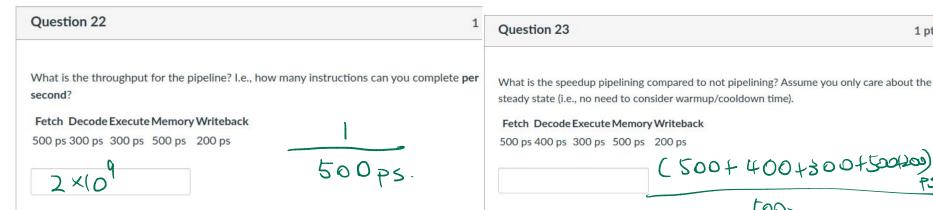

Fetch Decode Execute Memory Writeback

500 ps 400 ps 300 ps 500 ps 200 ps

(500+400+300+5001209) PS

1 pt

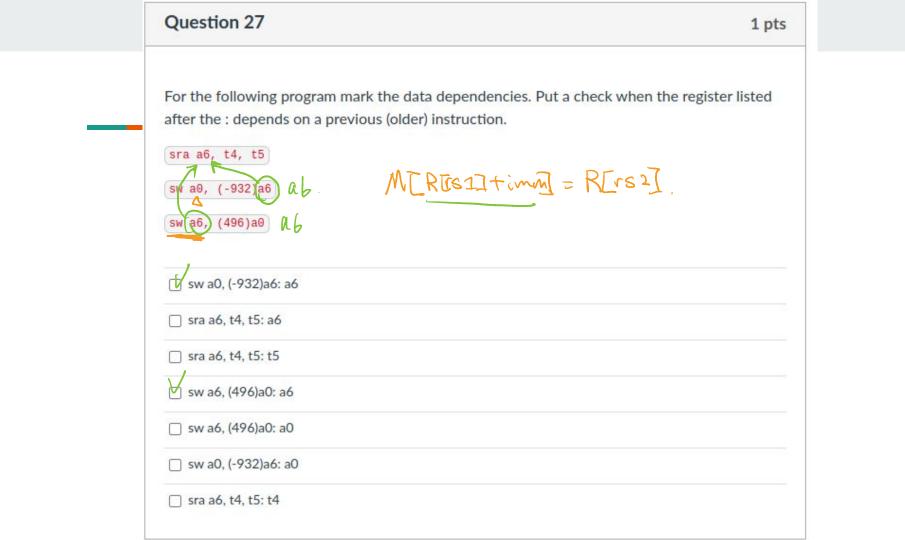

xor s6, a4, t0: a4

1 pts

after the : depends on a previous (older) instruction. xor s6, a4, t0

| lw s7, (-4)t6        | VCIOT |  |

|----------------------|-------|--|

| lw t6, (256)s6: s6   |       |  |

| ☐ Iw s7, (-4)t6: s7  |       |  |

| xor s6, a4, t0: t0   |       |  |

| xor s6, a4, t0: s6   |       |  |

| ☐ lw t6, (256)s6: t6 |       |  |

| lw s7, (-4)t6: t6    |       |  |

| Question 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Question 31                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| In which stage do you know you need to stall for a control hazard?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | When predicting a branch, you need to predict which two thing |

| ○ Writeback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | the target address                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | if it is an exception                                         |

| 000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 1000 100 | forward or backward                                           |

| ○ Execute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | number of cycles to stall taken or not taken                  |

| ○ Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                               |

| ○ Fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | which stage it is in                                          |